Knowledge facilities and AI chips are hitting limits in pace and effectivity. Can a 64 Gbps bi-directional interface change efficiency, lower energy, and scale back chip dimension?

Knowledge facilities and chip designers face a problem. They should transfer extra information at increased speeds whereas preserving energy use and chip space in examine. As workloads develop for AI and different compute functions, conventional interconnects are hitting limits in bandwidth, effectivity, and reliability.

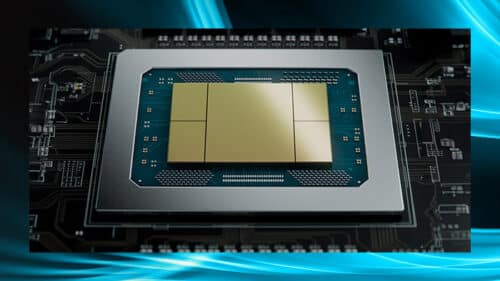

Marvell 64 Gbps Bi Directional Die to Die D2D Interface has been developed to deal with this. It’s constructed on a 2nm course of node and in addition out there in 3nm. It provides subsequent era XPUs a option to join compute dies. Every wire within the interface can carry 32 Gbps of two-way information, serving to designers push efficiency with out the penalty of upper power use or bigger silicon space.

The expertise delivers over 30 Tbps per millimeter of bandwidth density, greater than 3 times that of UCIe at comparable speeds. Its design reduces compute die space by as much as 85 % versus typical interconnects, whereas adaptive energy administration lowers interface energy use by as much as 75 % in regular operation and 42 % beneath peak masses.

Marvell has in-built reliability options comparable to redundant lanes and automated lane restore to scale back bit errors and enhance yields. To make adoption simpler, the corporate gives not simply the D2D PHY however a whole stack together with the applying bridge, hyperlink layers, and bodily interconnect. This offers chip designers a platform for constructing the following wave of XPUs.

This product is geared toward chip designers and semiconductor corporations engaged on subsequent era XPUs and processors. It’s helpful for groups designing AI accelerators, information middle processors, and different compute methods that want sooner die-to-die communication whereas minimizing energy use and chip space.

“The 64 Gbps bi-directional D2D interface IP marks an trade first and displays our dedication to pioneering applied sciences that improve efficiency whereas decreasing whole value of possession for next-generation AI gadgets,” mentioned Will Chu, senior vice chairman of Customized Cloud Options at Marvell. “D2D interfaces—which kind the spine of the communications networks linking silicon die throughout the similar system–are basic to rising the efficiency and effectivity of knowledge middle semiconductors and particularly the quickly rising customized computing section,” mentioned Baron Fung, Senior Director of Analysis at Dell’Oro.