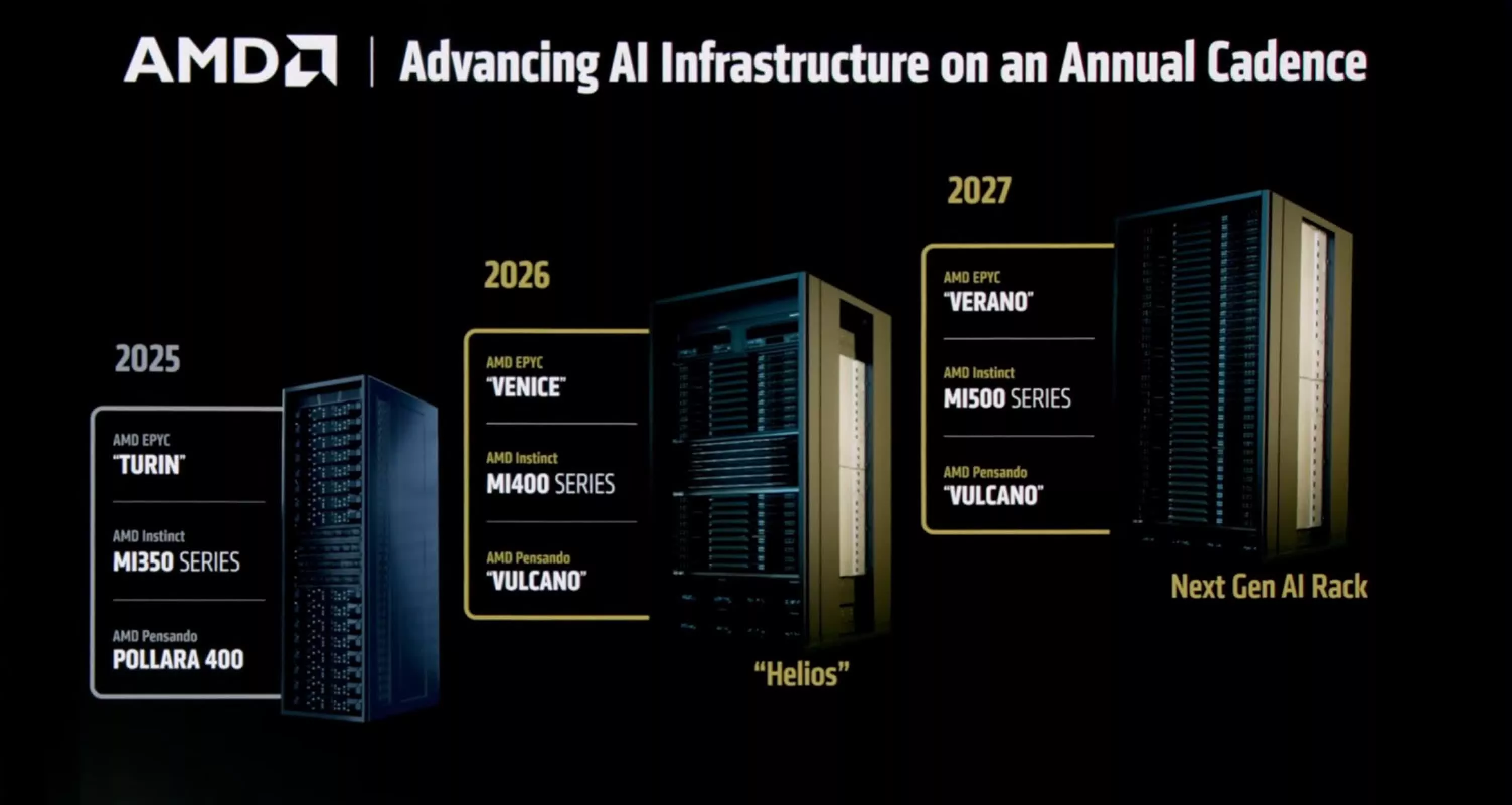

What simply occurred? AMD is getting ready to shake up the information heart panorama with its forthcoming Epyc Venice processor, a chip that guarantees to set new requirements for efficiency and scalability in server computing. Introduced on the firm’s current Advancing AI occasion, the Venice CPU is constructed on AMD’s next-generation Zen 6 structure and is slated for launch in 2026, concentrating on the ever-increasing calls for of synthetic intelligence, cloud computing, and high-performance analytics.

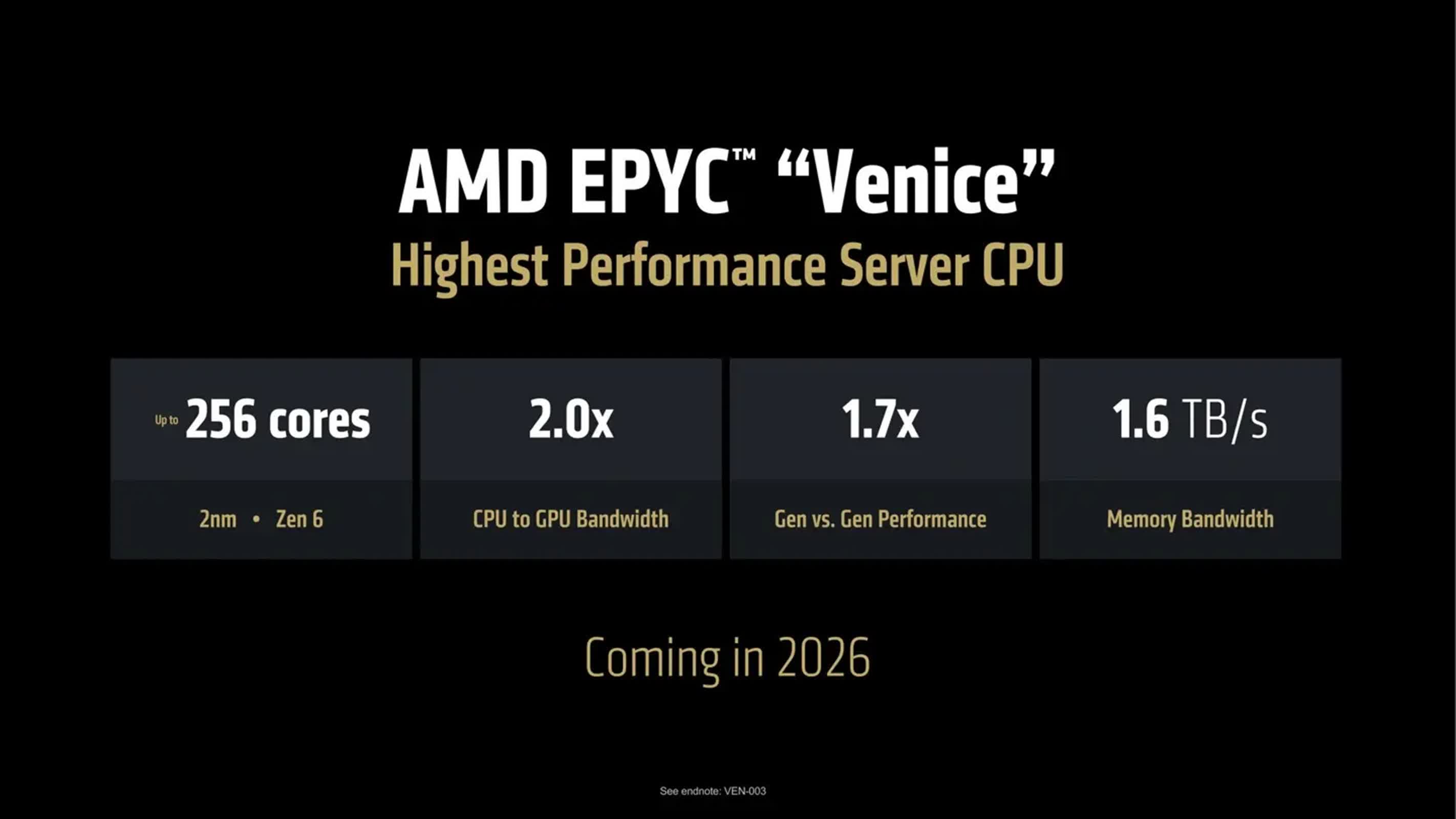

Venice makes a dramatic leap in processing energy. The chip will assist as much as 256 Zen 6 cores, a 33 p.c improve over the present Epyc Turin processors, which prime out at 192 cores. AMD additionally claims that Venice will ship as much as 70 p.c greater efficiency in comparison with its predecessor, an achievement that stems not simply from extra cores, but in addition from vital enhancements in per-core effectivity and architectural enhancements.

The technological basis for these good points is TSMC’s superior 2-nanometer manufacturing course of. By skipping instantly from 4nm to 2nm, AMD can pack extra transistors into the identical silicon space, boosting each efficiency and power effectivity.

Reminiscence bandwidth is one other space the place Venice stands out. The processor will greater than double the per-socket reminiscence bandwidth to 1.6 terabytes per second, up from 614 gigabytes per second within the present lineup. That is anticipated to be achieved via a mixture of assist for as much as 16 channels of DDR5 reminiscence and compatibility with superior reminiscence applied sciences similar to MR-DIMM and MCR-DIMM. These enhancements are essential for feeding information to the massive variety of high-performance cores, particularly in data-intensive workloads widespread in AI and analytics.

AMD can be addressing the rising want for quick communication between CPUs and GPUs. Venice will double the bandwidth for CPU-to-GPU communication, seemingly by adopting PCI Categorical 6.0. With as much as 128 PCIe lanes, the brand new platform will be capable of transfer as a lot as 128 gigabytes of information per second in every path, not counting encoding overhead. That is notably vital for AI coaching and inference, the place fast information motion between processors and accelerators is important.

The Venice processor will debut on AMD’s new SP7 platform, which is designed to accommodate the elevated energy and I/O calls for of the chip. The SP7 socket is anticipated to assist greater energy supply – doubtlessly properly past the 700 watts supported by the present SP5 platform – and permit for extra compute complicated dies on a single package deal. This new infrastructure may even allow extra reminiscence channels and higher growth capabilities.

AMD plans to supply Venice in two important variants: an ordinary Zen 6 model with as much as 96 cores and a high-density Zen 6c model, scaling as much as the complete 256 cores, each of which assist as much as 512 threads.

Wanting forward, Venice will anchor AMD’s Helios rack-scale structure, which can combine the brand new CPUs with next-generation Intuition MI400 GPUs and superior networking options. This technique is anticipated to ship a considerable leap in AI efficiency and reminiscence capability, setting the stage for much more highly effective platforms within the years to comply with.