That includes built-in AI acceleration, superior error correction, and near-threshold operation, it delivers unmatched power effectivity for always-on units—from wearables and drones to sensible IoT programs—ushering in a brand new period of clever, battery-optimized design.

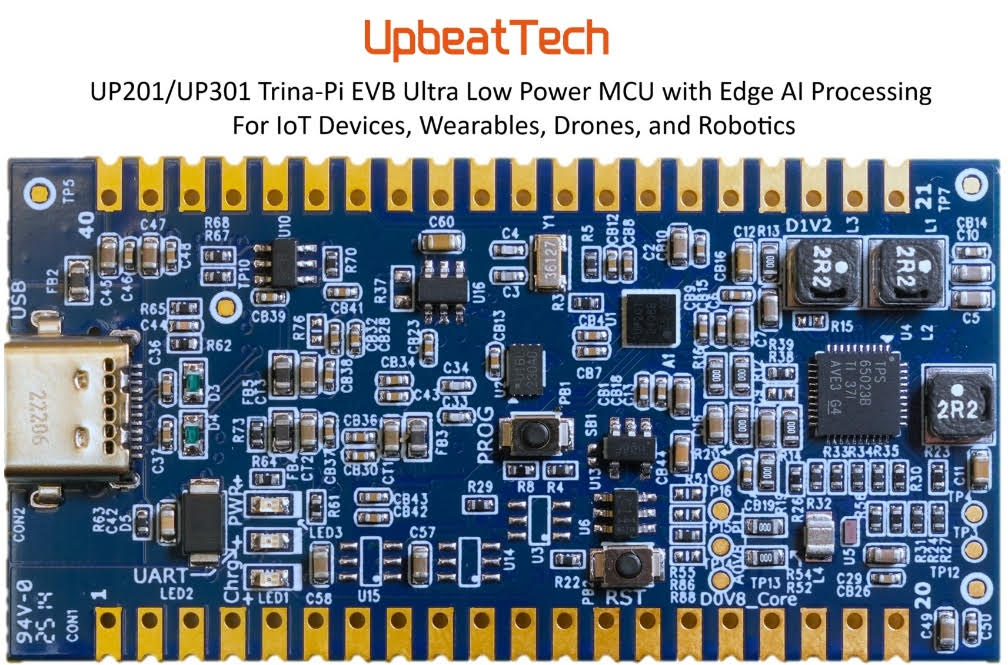

Upbeat Know-how and SiFive have teamed as much as unveil the UP201/UP301 MCU household—a dual-core RISC-V microcontroller platform designed to push the bounds of low-power intelligence on the edge. The chips mix SiFive’s Important IP cores with Upbeat’s proprietary AI acceleration and energy administration applied sciences, aiming squarely on the subsequent wave of battery-powered units.

On the core of the brand new MCU household lies a heterogeneous dual-core RISC-V structure paired with twin AI accelerators that promise a step-change in power-to-performance effectivity. Constructed for always-on IoT, wearables, drones, and sensible sensing programs, the UP201/UP301 platform delivers an ultra-low power profile of 16.8 μW/MHz/DMIPS—making it probably the most environment friendly edge processors in its class. Upbeat’s patented Error Detection and Correction (EDAC) and SRAM optimization additional improve resilience below near-threshold operation.

The important thing options are:

- Operates as much as 400 MHz with 717 DMIPS efficiency

- Optimized for edge AI workloads together with inference, sensor fusion, and DSP-based sign processing

- Delivers excessive compute energy with ultra-low power use, outperforming typical ARM-based MCUs

- Permits builders to construct smarter, battery-efficient AI functions on microcontrollers

In a preview of real-world efficiency, early adopters like Awan-sensing have reported exceeding energy targets whereas sustaining real-time responsiveness. The mixing of AI accelerators and DSP co-processing permits builders to run richer fashions, prolong responsibility cycles, and enhance consumer experiences—all with out draining battery life.

SiFive’s partnership performs a vital position on this innovation story. By leveraging its Important Household of RISC-V cores, SiFive helps Upbeat ship a platform that embodies the open-source {hardware} ecosystem’s promise: scalable, versatile, and energy-aware design for the clever edge.

Reside demos on the RISC-V Summit will showcase the MCU alongside Upbeat’s ultra-low-power MEMS Bone Conduction Microphone, with classes diving into heterogeneous RISC-V edge AI design. Engineering samples, SDKs, and reference sources are already obtainable, setting the stage for a brand new period of environment friendly, AI-ready microcontrollers.